-

SerDes 1/16MS Dairy/MS study 2023. 1. 17. 01:43반응형

내가 갈 연구실의 교수님과 상담을 하고 나서 연구 주제를 듣고, 교수님께서 e-mail로 내가 봐야할 개념들에 대한 영상과 keyword를 알려주셨다. 그래서 공부를 시작했어야했다.

하지만 12월에는 기말고사 시험을 마무리하고 조금 휴식기간을 가지고 일본여행을 준비하고 다녀오는데에 시간을 다 썼다. 그래서 1월이 돼서야 조금 마음을 잡고 계획을 수립하게 되었는데, 처음보는 분야라 막막하게 되었다.

시작은 SerDes 였다.

일단 두려웠던 것은 ㅋㅋㅋ 내가 싫어했던 통신분야가 섞여있던 점이다 ㅠㅠ

그리고 오랜만에 공부를 하려고 맘 잡으니까 집중이 잘 안되고, 시간만 버리고 집에서 뒹굴거리는게 일상이 되었다...

그렇게 1월 1주차를 버리게 되고, 2주차부터 마음먹고 하루 공부한 내용을 매일 블로그에 정리를 해보자 했지만, 공부를 했지만 정리하는데에 귀찮음이 생기고, 블로그만 작성하고 매크로 돌리는데 집중이 쏠려서 제대로 하지를 못했다 ㅠㅠ

또 내가 설날에 쉴 걸 생각하느라... 집중을 잘 못했다 ㅠㅠ

그리고 '재벌집 막내아들' 보느라 ㅋㅋㅋ

그렇게 1월 2주차부터는 교수님이 보내주신 Guideline에 따라서 따라가보려고 했다.

논문을 읽어보기 전에 SerDes관련 지식 습득을 위해 유튜브 영상 추천

1.

Alphawave IP: 전부 다 보고 나면 high speed wireline에 대해 웬만한 기본적인 background knowledge는 다 쌓을 수 있을 것이라 예상

Link: https://www.youtube.com/@AlphawaveIP/videos

*Alphawave IP: 고속 wireline interface 설계 전문 팹리스 회사로, synopsys, ARM, Cadence 다음으로 회로 IP 라이센스 세계 시장 점유율 4위

2.

Xilinx (now AMD): ADC-based wireline tranceivers

Link: https://www.youtube.com/watch?v=Ug-6HUgbWQk&t=3937s

3.

high-speed wireline transceiver, ADC-based SerDes 등의 키워드로 검색해가며 이런저런 정보

MATLAB에 최대한 익숙해지도록, verilog HDL 연습

Intel FPGA를 사용해 볼 기회가 있다면 써보면 좋을 듯Alphawave IP

Alphawave is a team of technology industry veterans and engineers with a nearly 20 year history of building successful Silicon/IP teams. Founded in 2017, Alphawave has already seen strong success and impact in delivering proven Silicon in leading 7nm proce

www.youtube.com

- PCI Express (특히 PCIe 5.0, PCIe 6.0)

- PCIe functionalities

- Datacenter top-of-rack (ToR) switch

방학때 모든 것을 숙지하라는 것이 아니라 이야기가 통할 수 있게끔 관련 키워드들에 대해 어느정도의 정보 숙지

공부한 것들이 있다면 QnA (시간이 많이 지나지 않았으니 없어도 됩니다), 그리고 연구내용에 대한 이야기 진행 예정

이처럼 e-mail을 받고 Alphawave IP 의 영상부터 보려고 했다. 하지만 아예 기초도 모른 채로 영어로 된 영상을 본다는 것은 나에게 무리라고 판단했다 ㅋㅋㅋㅋ.... 심지어 영어도 잘 못하는데 ㅠㅠ 영어 공부도 해야한다 ㅠㅠ

그래서 처음에는 한글로 정리한 블로그를 보고 간단한 지식을 쌓게 되었다.

Link : https://blog.naver.com/techref/222009286458

Simplex(단방향), Half Duplex(반이중), Full Duplex(전이중) 통신방식 비교

다음의 3가지 모드의 전송방법이 있다 - Simplex (단방향) - Half Duplex (반이중) - Full Duplex (전...

blog.naver.com

이 블로그가 그나마 유용하게 도움이 되었다.

그래서 지금부터 공부한 내용을 정리해보려고 한다.

또한 설 이후에는 꼭 매일 공부하고 글을 작성하는 것을 목표로 할 것이다!!! 화이팅!!

그리고 학부생때의 기억을 되살려서 PPT도 제작하면서 발표형식으로 만들 것이고, 책을 읽으면서 학부생때의 경험을 나만의 글로 작성해볼 생각이다.

일단 SerDes 라는 것은 'serialize와 Deserialize' 를 뜻하는 용어이다.

현재에서 가장 많이 쓰이는 것으로 I/O 핀 수와 interconnect 수를 축소하는 것에 목적이 있고, 대역폭 절약에 장점이 있다.

고속 Serial 통신을 위해서 SerDes를 쓰는데, 제한된 입출력 보상으로 고속통신에서 쓰는 Function Block의 형태로 존재하는 하나의 Module인 셈이다. 결과적으로 직렬/병렬을 자유자재로 바꿔주는 것이다. 그렇게 다양한 분야의 Interface로 지칭이 된다고 한다.

Q. 여기서 의문이 생긴 것이 근데 그냥 병렬로 Serial 속도 똑같이 해서 빠르게 속도에만 초점을 두게 못하는 건가?? (왜 굳이 직렬로 바꿔서 통신을 하는 것인지 의문... 교수님께 질문 예정) (나중에 가면 한심한 질문일 수도 있겠지만 지금은 직렬의 의미를 잘 모르겠다)

기본적으로 SerDes가 PISO와 SIPO가 존재하는데 'parallel input serial output' 과 'serial input parallel output' 를 의미한다. (이 부분의 구조에 대해서는 아직 잘 모르겠어서 추후에 serdes architecture를 찾아서 공부하면서 RTL은 어떤식으로 구성이 되어있는지 찾아봐야할 것 같다)

이렇게 두개의 function block으로 병렬과 직렬을 바꾸게 된다. 내부 구조로는 Metastability라는 불안정한 state를 방지하기 위해서 이중버퍼를 사용하며 (SIPO는 더 느린 병렬측의 데이터보관) 단일 shift register로 구성이 되어있다.

PLL을 통해서 (serial이 더 빠른 주파수) 병렬 clk을 직렬 주파수 크기까지 곱셈이 가능하다고 한다.

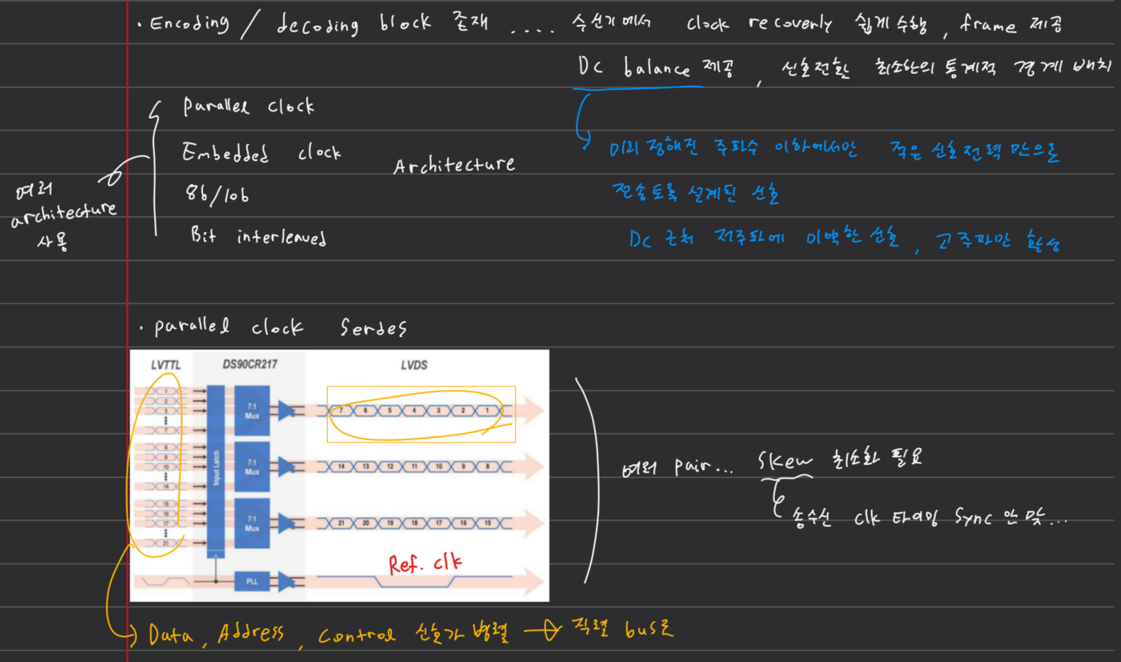

Encoding / Decoding block이 SerDes에 포함이 되어 있다고 하는데, 대표적으로 4가지 구조가 존재한다고 한다.

이런 block들이 Rx 측에서 clock recovery를 쉽게 수행을 하게 도와준다.

cf) DC balance 란, 미리 정해진 주파수 이하에서만 적은 신호 전력만으로 전송하도록 설계된 신호로 DC 근처 저주파에서 미약한 신호와 고주파에서 활성화되는 신호이다

이런 block들은 신호전환에 있어서 최소한의 통계적 경계 배치되어있다.

먼저 parallel clock serdes를 보면, 위의 그림과 같이 Data, Address, Control 신호가 병렬에서 직렬 bus로 변환이 되는 과정에 Reference clock이 존재하고 여러 pair가 있게 된다. reference clk에 있어서 송수신의 Clk sync가 잘 맞아야한다.

(뒤에서 한 번 더 언급 예정)

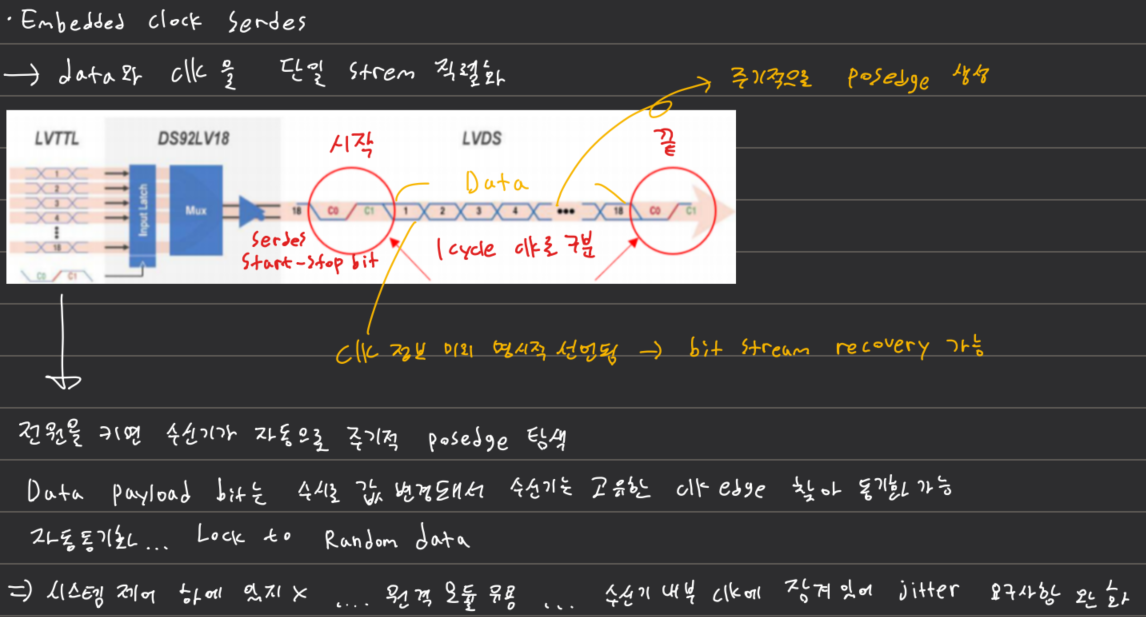

두번째로 Embedded clock Serdes 구조도 있다. 이는 data와 clk을 단일 stream으로 직렬화함으로써 PLL의 추가 신호선이 없어도 된다. 주기적으로 posedge를 생성하고 clk 정보를 미리 명시적으로 Rx 측에 선언이 되어있어서 bit stream recovery가 가능하다.

전원을 키면 수신기가 자동으로 주기적으로 posedge를 탐색한다. 자동 동기화가 되는 셈으로 Lock to Random data로 data를 오류 없이 잘 받아낼 수 있다. 시스템 제어 하에 있지 않기에 원격 모듈로 유용한 구조로 수신기 내부의 clk에 의해 잠겨 jitter 요구사항을 완화시킨다.

수신기에게 시작과 끝을 알리는 clk이 따로 bit로 존재한다.

세번째로 8b / 10b serdes로 일반적인 인코딩방식이다. byte 단위의 data를 직렬화 전에 10bit code에 매핑시키게 된다. Rx에서는 기준 clk으로 복구된 clk을 모니터링하게 되며, DC balance를 지원하고 frame 기능을 제공한다.

(이러한 구조를 정확히 다시 알아볼 필요가 있을듯....)

마지막으로는 Bit interleaved Serdes 가 있다. 여러개의 직렬 stream을 더 빠른 직렬 stream으로 바꿔서 multiplexing 하여 보내는 형식이다.

그 다음으로는 LVDS가 계속해서 언급이 되어서 LVDS인 디지털 표준에 대해서 찾아보게 되었다.

LVDS는 Low voltage differential signaling 의 약자로 저전압으로 차등 전압으로 신호를 확인하는 형태이다. differential의 형태는 single node에 비해 노이즈에 강하다는 장점이 있다. 그래서 계속해서 LVDS가 디지털 신호의 표준으로 직렬 통신 장거리 interface로 사용되었다.

EMI (electronic magnetic interference) 도 줄일 수 있고 serdes 사용...

아무튼 이런 LVDS 관련으로 PCIe가 등장하게 되는 것이다.

(추후에 LVDS와 PCIe 다룰 예정)

LVDS는 위의 그림 처럼 1.2V를 기준으로 차등으로 0/1을 구분하게 되어서 common voltage에 대한 noise 감소에 우수하다. 350mV 전압차로 계속해서 변화하게 되고, 아래의 사진처럼 Driver가 3.5mA의 전류원으로 구성이 된다.

다시 Serdes를 찾아보게 되었다.

(나는 약간 반복하면서 더 깊게 들어가는 스타일로 공부를 하면 나중에 깨달음이 찾아온다 ㅋㅋㅋ... 그래서 좀 느림..)

아무튼 결론적으로는 직/병렬 변환장치이며, 직렬을 이용함으로써 대역폭을 절약할 수 있다고 한다. 또한 I/O 핀수를 줄이면서 connector를 얇게 유지할 수 있는 셈이다.

데이터 속도에 관해서 점차 발전해서 최근에는 224Gbps까지로 발전된 것을 알 수 있다. (나는 아마 이 부분으로 DSP를 연구하거나 DataCenter Rack에 관해서 연구하지 싶은데, 조금 더 끌리는 쪽은 DataCenter이다. 근데 어려울 것 같은 ㅠㅠ)

아무튼 이렇게 발전해오는 과정에서 ISI (intersymbol interference)의 영향을 해결하는 것이 컸고, 그로 인해서 Equalization의 등장과 eye diagram이 등장이 시작된다.

그렇게 내가 해결해야할 키워드가 ISI, jitter, NRZ modulation(encoding), PCIe, DSP technique, Equalization 등이 있지 싶다. DSP 관련해서 신호처리 수업을 조금 찾아봐야할 것 같다 ㅠㅠ

이번에는 처음으로 Eye diagram에 대해서 정보를 얻기 위해서 공부를 해봤다. eye diagram은 error에 대한 체크를 위한 diagram으로 signal tracing을 통해서 신호의 noise를 확인한다.

time domain으로 진행이 되고 variation을 수집하는 것이다. data를 전기적 관점에서 오류를 체크하며 eye mask로 비교를 할 수 있다. 그렇게 BER (bit error rate) 로 확인이 가능하다.

Eye diagram의 기준은 여러개가 있다. 일단 신호가 겹치는 부분을 jitter라고 한다. (cross-over region) 그리고 VH와 VL을 지정하여 Eye amplitude를 지칭하고 Eye height도 지정해서 eye open 정도를 체크할 수 있다.

여기서 UI 라고 하면 unit interval로 하나의 bit를 인식하는 간격으로 볼 수 있다.

그 다음으로 Eye width를 볼 수 있고, fall/rise time인 edge rate이 존재한다. jitter가 크면 eye width가 작아져서 다른 수신기에 영향이 갈 수 있다.

그러고 Eye mask를 확인해서 저 영역에 violation이 없어야만 하는데, 이를 통과하기 위해서 high speed signal conditional을 이용하는 protocol이 있는 것이다.

Eye diagram을 통해서 신호의 전송과정을 보면 신호가 감쇄되는 것을 볼 수 있다. 그렇게 eye diagram으로 최적의 sampling time과 신호 개선을 해야하는 것이다.

이번에는 이어서 die의 packaging 기술에 대해서 간략하게 공부해봤다.

Silicon interposer (여기서 interposer은 공정에서 연결하는 선) 은 Die to Die로 연결이 되는 것이다.... (사실 이부분은 조금 이해를 하지 못했다) 그러고 TSV 공정으로 뚫어서 선을 연결하는 방식이 있고, 이는 3D stack 방식이다. 마지막으로는 Wafer 단계에서 바로 연결을 해버리는 것이다.

interface에 대한 소개도 언급이 되었는데, 여기서 XSR이랑 USR에 대한 얘기가 있었고 HBM의 25배라고 하는데 이에 관한 구체적인 공부는 추후에 해야할 것 같다.

interface별로 loss와 속도에 관한 부분을 알아봐야겠다....

그러면서 serial link의 흐름과정을 나타냈는데, Serdes로 다른 device로 전송을 하기 위해서 channel (cable, backplane) 으로 전송을 하는 것이다. channel을 거치면서 감쇠가 일어나고 signal integrity effect 가 그 원인이다. 이렇게 감쇠된 신호를 Rx측에서는 equalizer로 보상을 해서 eye를 open 시켜야한다. 그러고 나서 S2P로 전환한다.

그런 신호에 대해서 다양한 Modulation scheme가 존재하고 그 중에서 집중해야할 것이 PAM4인 것 같다.

그렇게 Analog serdes와 DSP ADC serdes를 비교하였는데, 아직 정확히 이해가 되지 않기에 추후에 더 공부를 해야할 것 같다. 그래도 흐름상으로 DSP쪽으로 바뀌는 추세를 띈다고 한다.

그 과정에서 BW와 FIR filter에 대한 얘기가 나왔다.

그렇게 병렬과 직렬 통신에 대해서 비교를 하였는데, 병렬의 당연한 장점인 대량 통신이 가능하다는 점이다. 근데 이는 통신거리가 제한이 있다고 한다. 그래서 직렬 통신을 쓰게 되었는데, 구현이 쉽고 기존 선로를 활용이 가능하다고 한다. async형태의 통신에는 UART가 대표적으로 있고 RS-232가 있다.

Serial 통신으로 Baud rate과 BPS가 많이 나오는데, 이는 1초 선을 통과하는데 신호가 변화한 횟수를 의미한다.

이제 다시 LVDS와 Serdes 보게 되었다.

LVDS의 방식으로 여러가지가 있었는데, point to point 방식이 가장 보편적이며, 복수의 driver가 붙은 형식도 간간이 쓰인다. 하지만 이는 impedence matching이 힘들어서 reflection으로 인한 signal noise가 크다는 것이다. 그래서 multipoint 용으로 M-LVDS인 규격이 존재한다고 한다.

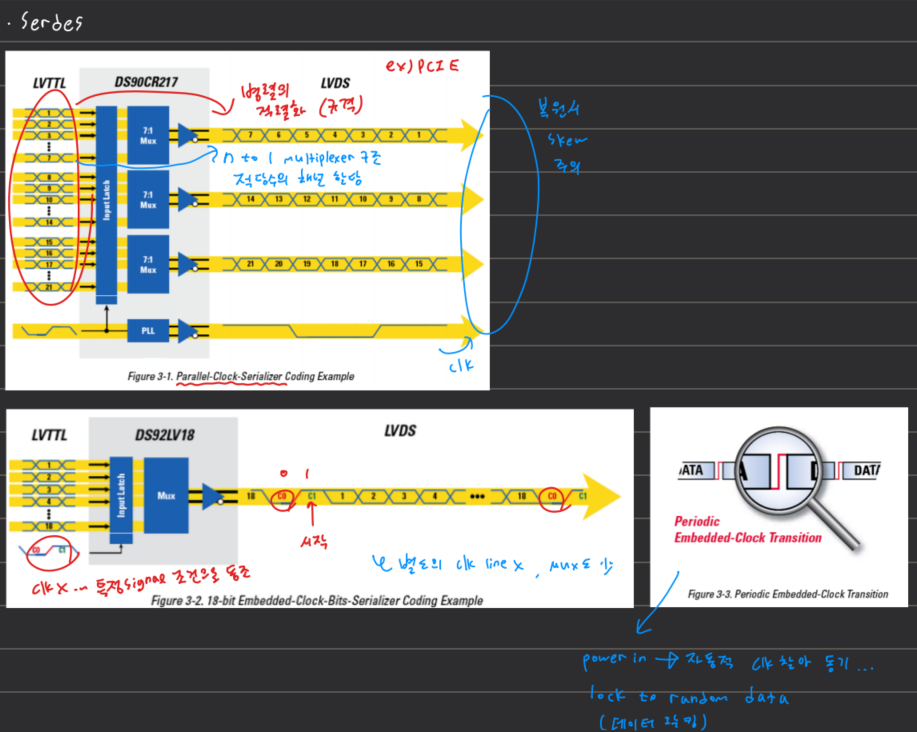

먼저 앞서 본 parallel clock serializer coding의 예시이다. n to 1 의 적당 수의 채널을 할당하여 Mux를 구성하고 규격에 맞춰서 직렬화를 한다. 하지만 이 경우에 clock을 보내서 받기에 Skew에 주의해야한다.

두번째로는 embedded clock 으로 특정 signal 조건으로 sync를 맞추는데 그래서 시작과 끝 신호가 존재한다.

별도의 PLL clk line이 없고 Mux도 적게 가져갈 수 있다.

적용하는 것을 보면 Parallel의 경우에 저전력으로 긴 전송거리의 장점이 있으며, chiplet에 따라서 bit가 다르다.

이는 Rack to Rack에서도 사용이 되는데, Serdes를 거쳐서 Rack으로 전송을 하는 것에 쓰임이 있다.

embedded의 경우에는 여러 data를 동시에 전송시에 유용하다.

8b/10b 는 byte단위로 진행을 하고 수신기의 제어권이 송신기에 없을 때 유용하다. 혹은 복수의 수신기를 지닐 때 유용한데, 새로운 수신기에 스스로 sync를 만들어서 끊이지 않고 data 통신이 가능하다.

그러고 DC balancing으로 ISI를 낮출 수 있다

FPGA에 연결하는 형태로는 Reference clock 없이 data를 자동으로 lock하여 byte 단위가 아닐 때 유용하다고 한다....

사실 이부분들이 꽤 이해가 안된다... 다시 계속 serdes의 구조를 찾아봐야할 것 같다.

그렇게 Serdes 구조 기술에 장단점을 볼 수 있었다.

이제 DSP serdes의 구조를 보게 되었다. 신호의 전달 과정을 간략하게 설명을 해놨는데, predistortion으로 Tx의 신호를 미리 emphasis하여 loss 와 attenuation을 방지 하는 것이다. 그러고 난 뒤에 Rx Equalizer에서 recovery를 하여 sampled 된 신호를 병렬로 보내게 된다.

PAM4의 형태도 살피면서 최근의 serial 통신의 속도를 보았다.

여기서 NRZ라는 개념이 나왔는데, 추후에 공부할 필요가 있을 것 같다.

또한 DSP serdes의 물리적 구조를 살펴봐야한다.

analog serdes에서 CTLE와 VGA 구조 예시가 있는데, 이는 Tx 측에서 보낸 신호를 미리 DC 영역은 유지하면서 고주파측에 gain을 늘려서 신호 감쇠를 방지하는 것이다. 그렇게 샘플링 nyquist frequency에 대한 gain을 올리고 VGA에서는 DC gain을 올려서 신호를 정확히 전달하기 위해 노력을 한다.

reflection에 대해서는 이후에 DFE (decision feedback equalizer) 를 통해서 처리가 가능하다.

digital Rx의 FIR (finite impulse response) filter를 통해서 tap별로 quantizing을 해서 응답을 구할 수 있다....

이런 구조상의 block은 다시 공부가 필요하다.

내가 느낀 바로는 quantizing이 되어서 analog에 비해서 ISI가 낮고 감쇄가 덜하다는 것...??

Timing recovery에 있어서 Mueller-Mueller (MM) 방식과 Minimal Mean Squared Error (MMSE) 방식이 있는데, current sample과 전후의 point로 error를 detect하는 것이 MM 방식이고 gradient를 통해서 찾는 것이 MMSE 방식이다.

DSP의 경우도 ADC로 양자화된 신호를 sample에 따라 pre-cursor와 여러 구조로 찾아낸다....

error를 찾고 recovery하는 부분도 추후에 공부하겠습니당....

아무튼 FIR filter를 거쳐서 slope을 근사화 하여 응답을 찾으면 오류를 matching 시켜서 깔끔하게 신호를 recovery가 가능하다는 것이다.

용어 정리로 잠깐 Data Rate을 보면 Baud Rate에 UI당 bit의 수를 곱하는 형식이다.

이는 PAM4의 경우는 4개의 신호를 사용하는데, 이게 UI당 2bit를 나타내서 data rate이 2배가 되는 것을 알 수 있다.

PAM2의 경우는 non return to zero로 NRZ라고도 하며 2개의 level을 지니는 것이 PAM4와의 차이이다.

그렇게 PAM2와 PAM4를 구분해서 볼 수 있다. full swing이 작아지게 되고 Nyquist frequency의 요구가 작아지게 되는 PAM4이다. UI당 2bit로 할당이 되어서 그런가??

아무튼 SNR은 9dB 안좋아지는데 이에 대한 답을 찾아야한다.

그렇기 때문에 PAM4에 대한 공부가 더 필요하다.

Q. PAM4가 PAM2에 비해 Nyquist의 요구 주파수가 낮은 것에 대한 이유? (사실 이건 PAM4를 더 공부하면 알 듯 싶긴 하다)

이번에는 광소자에 대한 얘기가 나온다. CPO로 co-package optical인데, chip 공정에서 optical 모듈을 합치는 것을 뜻한다. 이는 optical이 지닌 장점 때문에 일어나는 현상인데, 아직까지는 DSP를 대체할 정도의 기술은 아니라고 한다.

(참고로 CAGR은 연평균성장률이다)

그렇기 때문에 optical에서 다시 digital로 변환을 해서 신호를 전달할 필요가 존재한다. 그것에 관한 것이 Switch 인데, 이는 datacenter의 스위치를 칭한다.

(이 부분도 공부를 해야한다)

다시 한번 DSP Serdes의 흐름을 보면 바이트 단위의 데이터가 병렬로 들어와서 Tx를 통해서 pre-emphasis를 하여 ISI에 대해서 (인접 data symbol로 인한 영향) 보상을 한다.

그러면 Channel을 통해서 data가 진행이 되고 (cable이 주로) Rx Equalizer에서 고주파 loss에 대해서 filter와 같은 방식으로 overcome 해야한다.

이런 과정에서 Nyquist channel loss가 있는데, 이는 power 소모와 직결되고 serdes power 비중이 느는 태세이다.

그래서 전력소모를 유지하면서 BW(bandwidth)를 늘리는 것이 중요하다.

그렇게 CPO에 대한 것이 나오는데, optical에 대한 부분도 다시금 찾아봐야할 것 같고, 이에 대해서 나오는 XSR과 같은 intreface 형식에 대해서 공부해야할 것 같다.

추가로 I/O pad에 대한 chip간의 병목현상이 있는데, 그런 칩 구조 배치에 대한 설명이 있다.

I/O에 대한 얘기로 가면서 pin 제한에 맞춰서 BW를 증가시켜야 한다는 추세이다.

channel 통신을 하는데서 serial로 진행하여 BW를 늘려서 pin 수의 제한에 맞서야한다. 그래서 SerDes가 필요하다.

근데 고주파 통신에 있어서 loss가 발생하는 경우가 2가지가 있다.

첫번째로 skin effect이다. 고주파가 됨에 따라서 케이블의 표면으로 전류가 쏠리는 현상이다. 이는 단면적이 감소하면서 series impedence를 늘리게 되어 손실이 생긴다.

두번째로는 dielectric에서 전자기장이 빠르게 변화하여 heat up 하게 되어서 손실이 생기는 것이다.

그러한 loss들로 인해서 neighbouring pulse와 중첩이 생겨서 0인지 1인지 인지가 어렵게 되는 것이다.

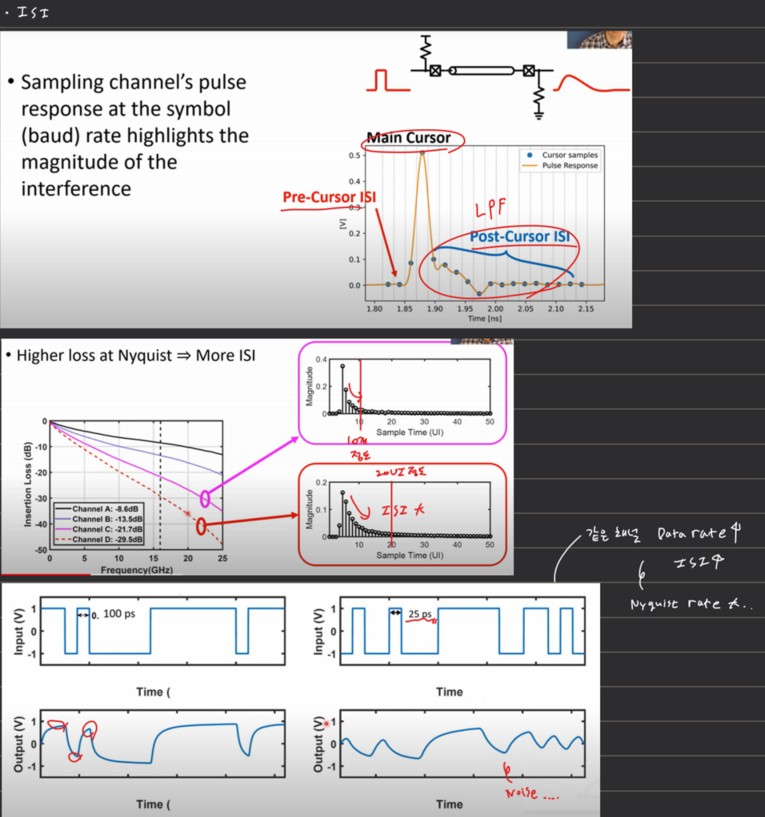

ISI에 대해서도 간략히 설명을 하는데, 더 자세히 공부할 필요가 있을 것 같다.

sampling에 있어서 main cursor와 pre/post cursor를 언급하는데, 이는 주변 cursor가 낮아서 중첩에 영향을 주지 않아야 한다. Nyquist에서 loss가 클수록 ISI가 더 커서 잡다한 신호가 많이 생긴다.

또한 같이 channel에 있어서 data rate이 크면 ISI가 커지게 된다. 즉 이는 Nyquist rate이 커지는 꼴이 되는 것이다.

속도가 빨라진다는 것이 주파수가 커지는 것이고, 이에 맞춰서 Nyquist frequency도 커져야하는 것이다.

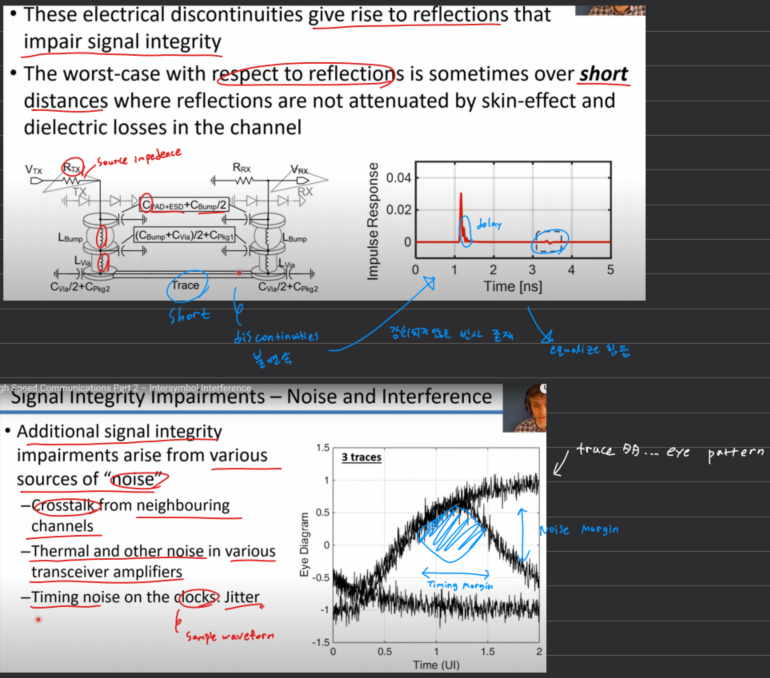

추가로 discontinuities로 인해서 package level에서 신호가 전달될 때 loss로 reflection과 또 다른 ISI가 있을 것이다...?

이런 전기적 불연속성은 reflection을 유도하게 된다. 특히 매우 짧은 거리에서는 감쇠되지 않는 반사로 인해서 equalize가 힘들다고 한다. 그렇게 eye diagram으로 체크가 가능하다.

equalizer를 제대로 공부해야겠다..

이번에는 간략하게 Serdes 구조들에 대한 흐름을 보게 된다.

distrete time에서 Tx의 Equalizer는 tap weight transmit filter로 weighted sum의 형태로 진행이 된다. (이런 구조를 제대로 공부해야겠다)

Rx측은 high pass termination network로 equalizer가 수행되는데 (HPF 느낌??) Continuous time linear equalizer로 회로는 위의 사진 처럼 구조가 되어있다.

PAM4에서는 nyquist loss에 대한 compensation이 필요하다....

그렇게 DSP Eq 측에서 FFE와 DFE로 ISI를 예측하여 제거를 한다고 한다.

약간 모든 가능성의 sequence를 찾고 error가 가장 적은게 actual 이라고 판단하는??

후.. 아무튼 이 ADC DSP serdes 구조는 더 자세히 알아볼 필요가 있다.

이번에는 Connectivity trend를 소개한다. die close together 트렌드는 복잡한 equalizer가 없어서 좋지만 power density가 크다는 단점이 있다.

그 다음으로는 dies far apart로 효율적 사용을 위해서 다 seperate 시킨 경우가 있고 seperate interconnect로 신호 무결성에 대한 어려움이 있다.

다음으로 direct attaching cabling과 repeater or cable이 있는데, cable을 직접 연결하다가 중간에 repeater를 넣어서 signal 무결성을 완화하는 것이 있다.

다음으로는 flyover cable과 optical interconnect으로 PCB가 필요없어지는 쪽과 광통신을 이용하게 된다. 광통신으로 인해 통신거리가 길어질 수 있다.

그래서 CPO 형태로 광통신을 같이 packaging하는 경향이 나타나는 것이다.

(CPO에 대한 추가 조사 필요)

high speed I/O bus가 고속을 위해서 serdes를 이용하게 되었고, 그에 대한 protocol로 PCIe가 나오게 되었다.

PCIe는 LVDS를 이용한 interconnect 이다.

crosstalk과 불연속성으로 인한 reflection이 jitter를 유발하는데, jitter는 BER에 중요한 역할을 한다.

Tx에서 전압 크기를 키우면서 고주파 채널의 loss를 보상하고, 3 tap FIR 로 극성 반전 전후로 다른 값을 취하게 해서 equalizing 하게 된다. 그에 대한 명칭이 위의 사진에 있으며, flat level voltage와 pre-shoot, de-emphasis 등이 있다.

이로써 Rx의 equalizing을 진행하는 것이다. 그렇게 다른 bit의 전압 level을 이용해서 수정을 하고 DFE 이후에 BER 복구를 진행한다고 한다.

휴... 이제껏 1주일 간 한 내용이고 이제 18일에 교수님과의 면담 전에는 alphawave 영상과 ADC DSP에 대한 영상은 마무리를 짓고, 남은 궁금증에 대해서 해결을 해야겠다...

질문

공부할것

핵심

'MS Dairy > MS study' 카테고리의 다른 글

Xmodel HSlink (5) (0) 2023.02.06 Xmodel HSlink (4) (0) 2023.02.06 Xmodel HSlink (3) (0) 2023.02.06 Xmodel HSlink (2) (0) 2023.02.06 Xmodel HSlink (1) (0) 2023.02.06