-

Xmodel HSlink (6)MS Dairy/MS study 2023. 2. 6. 22:06반응형

2일차에는 수업을 PLL부터 진행을 했다.

내가 가장 이해를 못했던 부분이었는데, 연구원분이 설명을 잘해줘서 나름 이해가 갔다.

PLL은 기본적으로 output clk과 input clk을 feedback을 통해서 align하는 과정이라고 한다. 즉 inout의 clk을 동기화해서 data의 sampling이 제대로 될 수 있도록 돕는 것이다. Voltage controlled oscillator를 통해서 phase와 frequency를 조절한다고 한다. (보통 높은 주파수를 뽑아서 feedback 비교는 낮은 주파수로)

synchronize two clock을 하는 방식은 phase offset의 비교와 frequency 비교가 있다. 설명을 할 때 예시를 들어서 설명을 해줬는데, 시간 차이가 10분 나는 것이 phase 차이일 수도 있고 frequency 차이도 있다는 것을 시계약속으로 설명을 했다.

시간을 맞췄는데도 다시 10분 차이가 나는 것이 애초에 한명의 시간 clk이 빠르거나 느린 것이니 그런 것이다.

몇분차이와 속도차이에 대한 error를 아는 것이 hard하기에... 주파수는 맞춰두고 위상만 조절하는 방식은 DLL(delayed locked loop)이라고 한다. 하나만 조절하면 되니 쉬운...??

DLL과 PLL에 대한 것은 좀 어려운 것 같다...

아무튼 reference clock이 있고 phase detector를 통해서 비교를 하게 된다. 그 뒤에 error를 가지고 filter를 거쳐서 frequency offset을 판단하고 phase offset을 조절하게 되는 것이다. VCO가 바로 출력하는 놈이다.

PLL의 구성 요소로 VCO가 있는데, 이는 output clock을 생성하고 원하는 phase와 frequency로 맞추는 것이다.

sensor로 PFD는 error를 측정하는 것이다.

Loop filter가 controller로 얼마나 조절을 해야하는지 control 하는 것이다.

그 중에서 charge pump PLL이라는 회로가 있다. 이는 RC filter를 합쳐서 설계를 하고 CP라고 한다.

여담으로 바퀴처럼 다음 판단에서 빨라서 바퀴가 뒤로 온지 느려서 뒤로 온지 알기 어렵다.

그렇게 PFD 즉 sensor를 보면 Phase-Frequency Detector로 두 신호 clock의 error를 측정하는 것이다.

기본적으로 두개의 flipflop으로 reset신호를 달고 있다.

Xmodel에서 gate primitive로 AND를 써도 되지만 1ps보다 작은 차이가 나면 알 수 없으므로 analog를 활용하게 된다.

그래서 simulation 결과 파형을 보면 clk2가 빨라서 점점 딸라잡는 신호인 것을 볼 수 있다. 처음에는 phase 차이가 나서 up의 신호를 주는데, 점점 phase를 따라잡게 되면서 down의 신호를 주는 것을 알 수 있다.

charge pump loop filter를 보면 up 신호가 들어오면 Isource로 전류를 뽑아주면서 Cp의 전압을 점점 올리면서 VCO로 인해서 V에 비례해서 frequency를 높이게 된다. 그러면 PFD에서 up을 요청해서 CP loop filter에서 V를 올려서 VCO에서 frequency를 올릴 수 있게 되는 것이다.

반대로 down pulse가 들어오면 Cp의 전하를 빼면서 V를 낮추게 된다. 중간 Cs가 series로 연결이 된 것은 전압의 급변화를 막기위해서 존재한다.

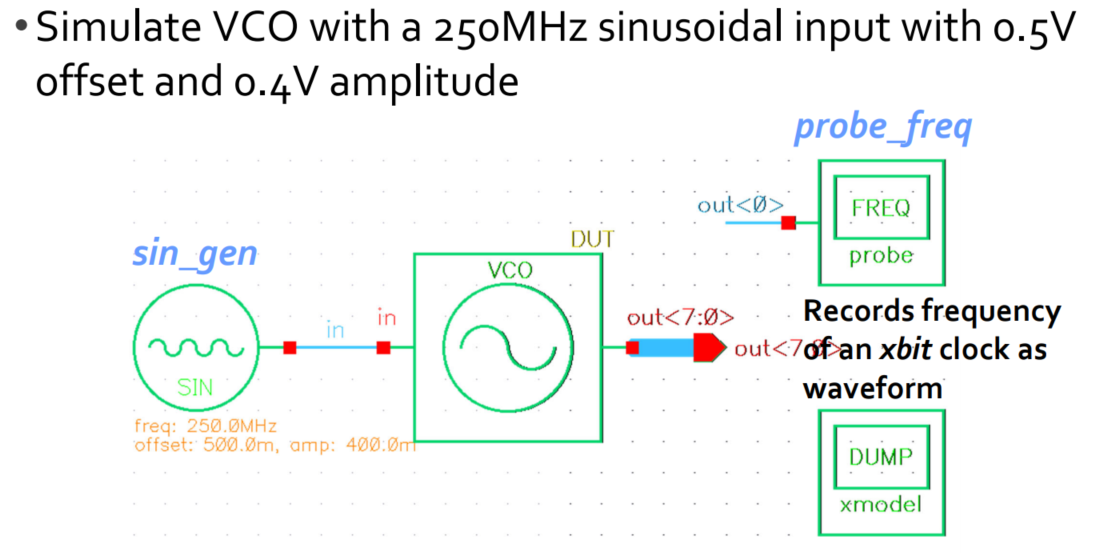

VCO는 functionality하게 보면 V와 f의 특성을 비례한 poly function으로 볼 수 있기에 Xmodel에서 functionality primitive를 사용할 수 있다고 한다.

어찌됐든 VCO는 1차함수 형태로 V와 f의 관계로 원하는 주파수를 출력으로 내보내는 셈이다.

그렇게 VCO는 8개의 phase clock을 뽑아낸다.

frequency divider는 reference보다 크게 원할 때도 있기에 serdes 분주처럼... 그래서 필요하다. 주파수를 높이는 것보다 낮추는게 쉽기에 필요하다. Divider는 보통 counter를 활용해서 설계를 한다.

그렇게 divide factor로 몇으로 분주할지 정할 수 있는 것이다. (clk마다 count하는 느낌??)

그렇게 각 모듈들을 합쳐서 PLL을 완성하게 된다.

PFD에서 up down을 측정하고 CP filter에서 V를 조정하고 VCO에서 V를 바탕으로 f를 조정하는 형식이다. 그리고 divider에서 원하는 reference로 조정한다. VCO의 출력은 8개의 phase로 나타나게 된다.

PLL은 s-domain에서 loop 해석을 할 수 있다. 그러면 damping factor와 같은 것을 구할 수 있고 이를 해석이 가능하다...

이러한 설계는 해석과 식에 맞춰서 설계를 할 수 있다.

그렇게 PLL을 적용해서 파형분석을 진행하면 vc 출력의 전압과 frequency를 볼 수 있다. 또한 phase를 locking 한 것을 볼 수 있다. 또한 divider가 잘 동작하는 것이 확인가능하다. 출력된 clk이 잘 locking하는 것을 확인!

이제는 locking된 clock이 과연 어떻게 잘 맞는지 아는지를 체크하는 파트이다. 이는 step response로 확인이 가능하다.

phase와 frequency의 step response를 보면 overshoot이 closed loop zero로 인해 존재하는 것이 보인다.

또 측정하는 것 중에 s-domain에서 sinusoidal jitter를 input으로 넣어서 SJ의 output 결과를 amplitude와 phase로 측정하는 것이다. 그러고 SJ 주파수를 sweep하면서 transfer function을 확인하는 것이다.

주파수를 바꾸면서 phase input을 하면서 주파수별 gain을 얻는 것이다. 그렇게 sinusoidal jitter의 통과여부를 체크하는 것이다.

그렇게 transfer function이 위의 조건에 맞춰서 나타난 것을 볼 수 있다. 즉 빠르면 신호가 못따라가서 locking을 제대로 못하는 것을 의미한다. sin jitter의 TF를 통해서 60Mhz까지가 최대라고 볼 수 있다.

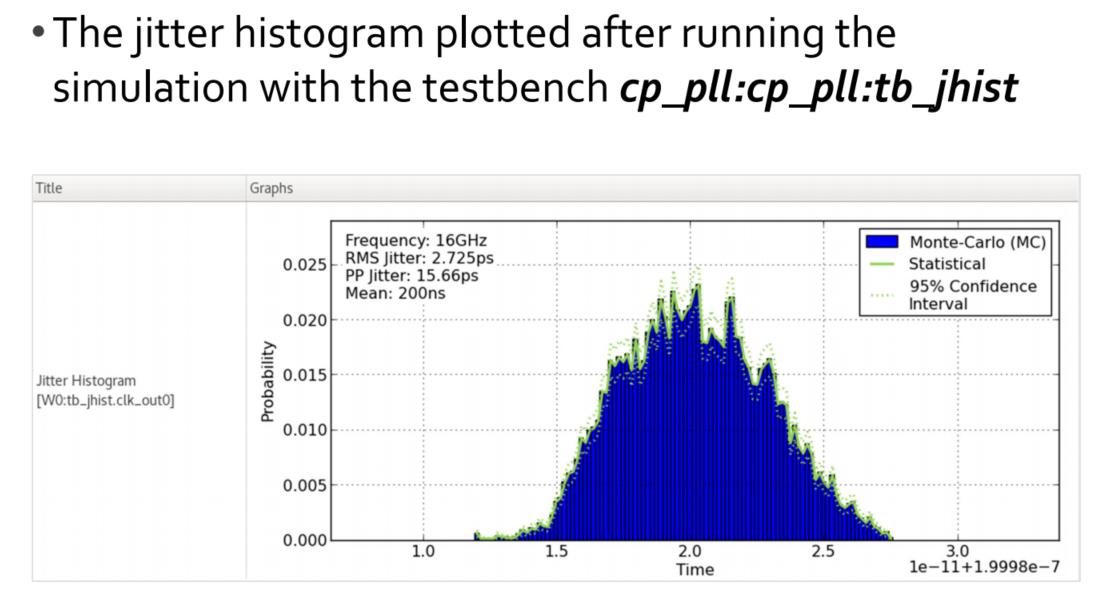

또 다른 측정방식으로 jitter histogram을 볼 수 있다. 그러면 대부분이 가운데에 모여서 있어야 좋은 것이다. 저 부분은 파형 변화의 jitter 부분으로 살짝씩 움직이는 지터의 분포를 나타내는 것이다. 그것이 모여야 jitter가 좋은 것을 알 수 있다.

마지막으로 charge pump의 current mismatch가 문제가 될 수 있다. UP과 DOWN의 pulse가 따로 있기 때문에 회로가 다르다. 그렇기에 흐르는 전류의 양이 동일하다고 보장할 수 없기에 disturbance를 유발하게 된다. 그래서 불규칙한 clock period와 reference spur을 만들게 된다. (up down pulse의 전류 비대칭으로 VCO의 clock 생성이 불규칙한 부분....)

그래서 misalign을 pulse를 늘려서 (전류가 적은 부분) 만들게 되는데, 이게 주기적인 ripple을 만들어서 voltage에 영향을 주게 된다. 그러면 harmonic 성분이 되는 것이다... 주기적인 jitter...

이러면 다른 주파수 영역을 침범하여 noise를 일으키게 된다.

이번에는 PLL에 대한 이야기로 어떻게 두 clock의 주파수와 phase를 조정하는지에 대한 이야기로 진행이 되었다. VCO와 PFD와 CP loop filter로 구성이 되어있는 PLL이 어떤 방식으로 파형을 만드는지 확인하면서, 측정에 대한 jitter도 확인을 하였다.

'MS Dairy > MS study' 카테고리의 다른 글

Xmodel HSlink (8) (0) 2023.02.07 Xmodel HSlink (7) (0) 2023.02.06 Xmodel HSlink (5) (0) 2023.02.06 Xmodel HSlink (4) (0) 2023.02.06 Xmodel HSlink (3) (0) 2023.02.06