-

Xmodel HSlink (7)MS Dairy/MS study 2023. 2. 6. 22:56반응형

이번에는 Clock과 data의 recovery에 대한 loop modeling을 배우게 되었다. CDR이라고 하며 clock과 data는 사실상 같이 복구가 된다고 한다.

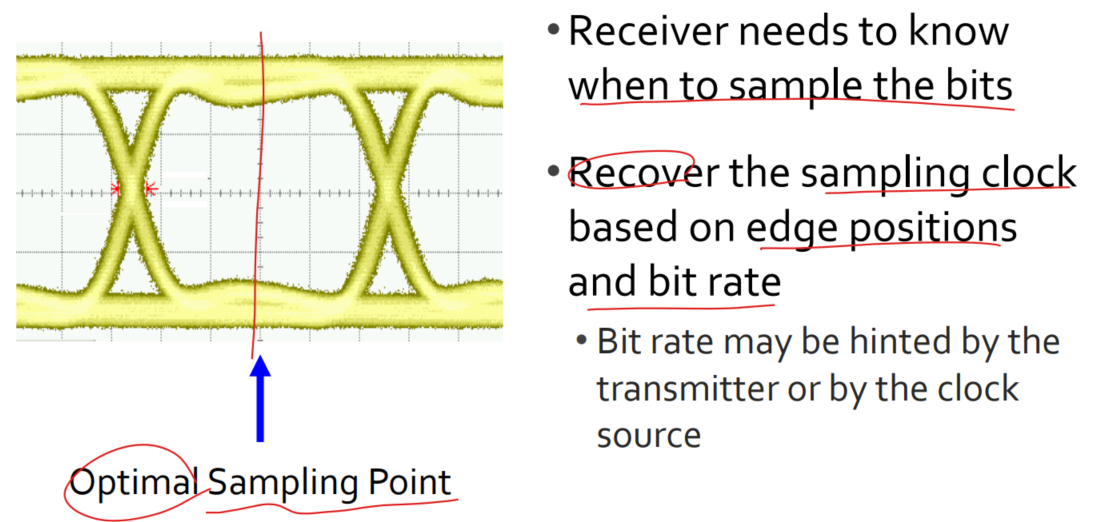

Rx측에서 data를 받을 때는 optical한 sampling point가 있다. 데이터 변화의 중앙에서 받아야 recovery가 적절할 것이다. Rx에서 sampling clock을 복구하는데 edge position과 bit rate에 base 되어있다.

Tx에서 신호를 보내는데 CDR은 간단하게는 PLL이나 DLL을 이용해서 RCLK으로 skew를 다시 복구하게 된다. 외부랑 위상이 동일하게끔 보정하는 것이다. 그렇게 delay를 상쇄하는 회로를 통해서 RCLK을 보내게 된다. 이는 송신측에서 sample clk을 보내서 sampling하는 것인데, 고속에서는 어렵다.

Mesochronous clocking은 frequency먼저 조정하고 phase는 다시 조정하는 것이다. phase를 받아서 측정하면 detector에서 error를 읽고 loop filter를 거쳐서 phase를 계속 조정해서 RCLK을 보내게 된다. 그것을 DATA와 비교를 하면서 진행을 하는 것이다. 그렇게 RDATA를 뽑아낸다.

plesiochronous clocking은 송신기가 clk을 보내지 않는 경우이다. 그냥 bpm hz만 정의해두고 진행하며 clk의 독립된 local ref로서 생성이 되고 위상과 주파수 모두 고치는 것이다. clk과 data는 같은 16Ghz여서 미세한 차이가 있다. CDR은 그래서 잘 tracking해야한다.

phase detection에 있어서 linear와 bangbang이라는 detection이 존재한다. data와 clk 사이의 위상차를 알아야하기에 먼저 linear를 보면 phase error를 선형적으로 뽑아낸다. 하지만 이는 고속으로 동작에 힘들다.

data를 받으면 up down pulse를 뽑는다. 그렇게 phase error를 측정한다.

여기서 full swing을 위해서 data를 DFF이나 xor과 같은 것을 거칠 수 있다.... 하지만 파워소모가 크다...

그렇게 simulation을 해보면 phase가 증가함에 따라서 주파수가 차이가 나는 것으로, 처음에는 down신호가 크게 있다가 (PD의 측정은 신호 변할 때만 알 수 있다... 비교를 하는 회로이므로) phase차이로 주파수가 빨라진 것처럼 느껴지면서 up pulse가 커지는 것을 볼 수 있다.

이제는 가장 많이 쓰이는 bangbang PD를 볼 수 있다. 이는 크기차이를 값이 아닌 부호로만 측정을 하기에 기능은 딸린다. 하지만 고속을 위해서 쓰이게 된다. 그래서 정보가 적기 때문에 비선형성을 띄며 PD를 Xsampler를 통해서 비교를 하게 된다. Data를 전후를 비교하고 Xsample 값을 비교해서 누구랑 같은지 보게 된다. 그렇게 transition 시에만 판별해서 late/early를 판단할 수 있게 된다.

CDR이 사실상 Rx의 역할로 bangbang PD를 보면 데이터 비교를 위한 비교기가 있고 기억장치인 DFF으로 엮어서 Xor로 전후 data와 누구랑 같은지 비교하게 된다. 그렇게 data를 뽑고 up/dn을 pulse로 보낸다.

그렇게 결과를 보면 phase가 증가함에 따라서 up pulse를 계속해서 출력으로 내게 된다. 전의 값이랑 같으면 빨리 샘플링을 한 셈이니까 dn pulse를 내는 것이다.

finite DLL로는 tracking을 할 수 없기에 360도랑 0도랑 구별을 못하는 것을 활용해서 infinite range DLL을 만든다. 메모리 인터페이스에 가장 많이 쓰인다고 한다.

위상과 주파수를 모두 고치려면 infinite range DLL이 필요하여 도입이 된 것이다. phase가 서서히 벌어지니... 그렇게 8개의 위상을... PLL을 써도 되지만 DLL 쓰려고...

먼저 feedforward interpolating CDR을 보면 PLL혹은 DLL을 생성해서 multiphase clock을 생성하게 된다. 그렇게 8개의 phase로 loop filter를 거친 select 신호로 2개의 phase를 뽑아내게 된다. 인접한 두개의 phase clock으로 phase interpolator를 하는데, weight에 맞춰서 phase를 각도를 얻어서 RCLK을 생성해서 PD를 통해서 다시 반복하게 된다. DATA와의 비교로....

그렇게 phase interpolating은 중간에 있는 각도도 사용하고 싶기에 나온 것으로 analog 부분과 digital 부분이 극명하게 나뉜다. CP-PLL로 clk을 생성하게 되면 8개의 phase clk을 mux를 거쳐서 뽑아내게 된다. 이에 대한 control이 clock out을 이어서 BB PD에서 loop filter를 거쳐서 컨트롤 신호를 뽑게 된다. data와 clk_out 값으로 계속 비교하면서 control하는 것이다.

그렇게 weight는 두개의 input phase를 short시켜서 전류의 세기로써 control이 가능하다. weight 값은 DAC를 거쳐서 digital control 신호로 analog 값을 넣어주게 된다. 2개의 mix 신호가 이와 같은 방식으로 생성되는 것이다.

이 경우에 16개의 up/dn 을 얻고서 다수결에 의해서 up/down을 결정하게 되게끔 block을 설계했는데, 이는 바로바로 체크하는 것은 변경이 되기도 전에 계속 반응을 하면 dithering이 너무 크기에 기다렸다가 결정을 하게 된다. 이 dithering이 전부 jitter로써 noise로 들어가기 때문이다.

그렇게 기다려서 다수결로 up/down을 결정하는 것은 decimation filter라고 칭한다. 이런식으로 CDR을 진행하게 되는 것이다. 즉 data와 RCLK을 맞춰서 sampling을 적절한 위치에서 할 수 있게 하는 것이다.

그렇게 파형을 보면 down의 경우에는 계속 control이 내려가서 한바퀴 돌아서 제한된 영역을 무한으로 확장한 느낌으로 볼 수 있다. 마찬가지로 up의 경우도 동일하며 이런식으로 infinite range DLL을 시행하게 된다.

phase interpolating의 testbench로 구성해서 살펴보면 phase가 locking하는 것을 볼 수 있다. 두번의 흔들림이 보이고 확대를 해서 보면 dithering이 존재한다.

먼저 PLL control로 VCO에서 vc값을 locking을 하고 (voltage frequency를 locking) PI에서 CDR에서 RCLK을 위한 up/down으로 비선형으로 infinite range DLL로 dithering하면서 ctrl 값을 locking하는 것을 볼 수 있다.

그렇게 결과적으로 전체적인 clk의 phase가 settle 되는 것을 확인할 수 있다.

posedge에 잘 sampling하는 것을 확인 할 수 있는 것이다.

jitter histogram을 보면 이전과 다르게 양쪽으로 퍼진 것을 볼 수 있는데, transition의 jitter가 중간에서 움직이는 것이 아니라 양쪽에서 움직이는 것을 확인하는 것이다. 이는 dithering으로 인한 것으로 간격을 줄일 필요가 있다.

또한 SJ의 TF를 보면 비선형으로 인해서 그 결과가 SJ의 amplitude에 따라서 변하는 것을 알 수 있다. SJ의 크기에 따라서 변화가 다 다르게 느껴지는 것으로 BW를 정할 수 없다. 같은 step으로 정량이 아닌 정성적으로 up/down만 판단하니...

그렇게 이번에는 Rx측의 data와 clk을 복구해서 sampling 하는 부분을 살펴봤다.

phase detection (PD)를 통해서 data와 clk 사이의 위상차를 복구하고

그중에서 가장 많이 쓰이는 bangbang (BB) PD를 알아보았다. 이는 PD가 중간을 체크해서 정성적으로 앞뒤의 신호로 느린지 빠른지만 체크한다.

그리고 phase interpolating (PI) 를 활용해서 phase를 DLL을 통해서 infinite range로 조정해서 control이 가능하게 하여 회로를 설계했다. phase 조정을 clk을 뽑고 그걸로 BB PD를 거쳐서 control해서 계속 phase를 mix해서 조절하는??

그렇게 dithering까지 알아보았다.

'MS Dairy > MS study' 카테고리의 다른 글

Signal Integrity - overview (0) 2023.02.10 Xmodel HSlink (8) (0) 2023.02.07 Xmodel HSlink (6) (0) 2023.02.06 Xmodel HSlink (5) (0) 2023.02.06 Xmodel HSlink (4) (0) 2023.02.06