-

SerDes 2/21MS Dairy/MS study 2023. 2. 21. 14:24반응형

열심히 해야지 싶으면서도, 설 이후로는 idec 강의를 듣는 것 외에 특별히 한 것이 없었다...

교수님과 면담을 하고 나서 다시 결정을 좀 해보려고 했는데, 교수님께서 바쁘셔서 내가 다시 공부를 했어야했다.

근데 안일하게 계속 생각하고 놀다보니까 벌써 다음주가 개강이다...

그래서 사실 좀 두렵다. 일찍 공부를 좀 했어야하는데... 그래서 다시 그 동안 잠깐 공부했던 것들을 적어보면서 계획을 수립해야겠다. 특히 영상을 다 보고 논문을 읽고 Matlab을 해봐야한다.

이번주에 오티도 있고 참 바쁠 것 같지만, 운동도 같이 병행하면서 열심히 해보면서 학교 생활에 적응을 해야겠다!!

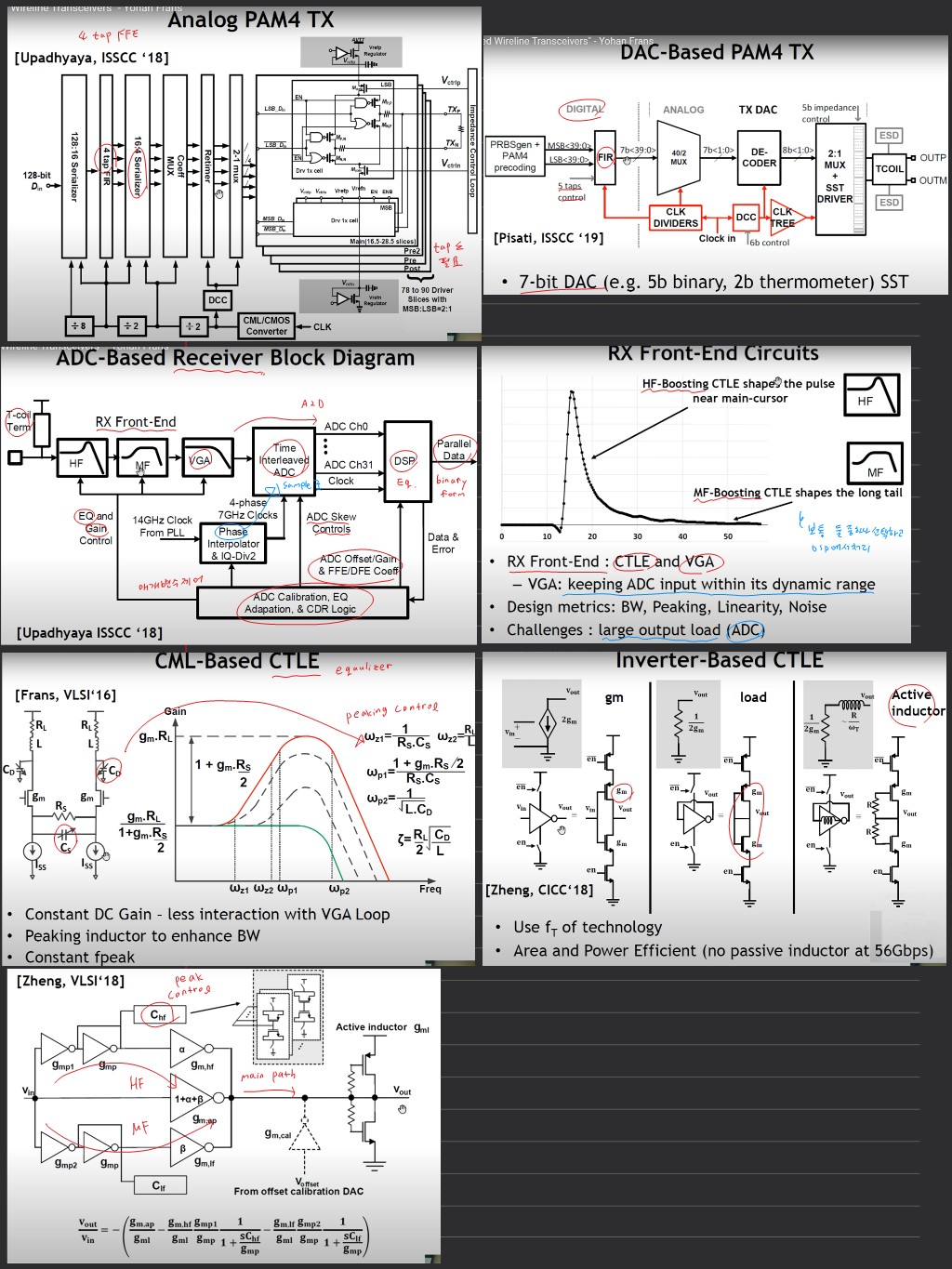

우선은 1달 전에 계속 보던 영상에 대한 이야기이다. PAM4에 대한 기본적인 이야기로 NRZ와 다르게 2bit씩 data를 가진다. 그래서 data rate이 2배가 되고 Amplitude는 유지한다. 그래서 SNR이 1/3이 되고 BW를 유지하게끔 PAM4를 구상했다.

PAM4에 대한 이야기는 다시 자세히 공부할 것이다.

이어서 Co-packaging Tech 에 대한 이야기를 하는데,

Die to Die (D2D) organic packaging 기판은 discontinuties 하다. SIlicon interposer는 배선 용이하게 공정을 하는 것인데, density가 증가한다.

이런 것들과 더불어서 여러 특성들이 있다. 이 부분은 추후에 필요할 때 챙겨보면 될 것 같다.

Die가 예시로 있는데, 각 pin에 data lane이 있고 row를 나눠서 data를 관리를 한다.

이런 패키징에 따라서 ISI에 대한 특성도 다르다.

또한 PLL을 통해서 Clk을 분배하는데 있어서, 거리에 따른 skew가 있을 수 있기에 performance가 중요하다.

그러면서 clock을 분배하는 방법이 여럿 존재하게 된다.

CMOS clock buffer에 따라서 PSIJ (power supply induced jitter) 가 존재한다. supply 전압과 비례하는 jitter로 buffer에 따라서 존재하는 것이다.

random jitter 는 RJ 라고 하고 rise/fall time이 길수록 noise가 커지고 그에 따라서 비례하는 것이다.

jitter impulse response에 대해서 분석이 있고, clk의 영향이 있게되며 이를 더 공부할 필요가 있다.

RJ가 input jitter에 convolution이 된 형태로 볼 수가 있는데, jitter가 입력으로 들어와서 시간편차 sequence 결과로 출력을 나타나게 된다. jitter impulse가 local edge에 영향을 가하게 되는 것이다.

또 jitter가 후속까지 영향을 미춰서 고주파에 왜곡이 큰 형태의 Transfer function을 볼 수 있다.

jitter impulse response가 증폭이 되는 것이다.

예시로 clock buffeer에 대해서 jitter를 보면, large buffer일 수록 Td (settling time) 이 작아져서 jitter가 낮고, buffer의 개수가 많아질 수록 RJ가 커지는 것을 볼 수 있다.

아무튼 결론적으로 clk 파형을 생성하는데 jitter를 고려해야하며, buffer의 개수와 크기도 고려사항이다.

modern serdes를 살펴보면 optical + electrical 을 combine 된 형태이다. 그래서 아직까지는 optical이 완전히 대체될 일은 없고 optical을 전기적으로 바꿔서 sampling해야한다.

analog front-end로 ADC가 필요하고 DSP로 이어서 serdes가 구성이 된다. 그래서 나도 DSP serdes를 자세히 찾아봐야한다.

그리고 serdes의 구성이 여러 필터가 필수적이다. 그러면서 impedance matching이 필요하고 termination을 하게 된다. LC ladder를 분배해서 artificial transmission line을 만드는 것이다.

fitler로는 equalizer가 CTLE/VGA 등 loss를 보상하고 ISI를 보상해서 eye 를 open 시키는 것이다.

여러 correction등이 있고, forwoar error correction (FEC)도 있으며 encoding을 longer bit로 해서 유효값을 얻고 error를 줄이는 것이다. 이게 바로 8-10bit encoder 인데, 최근 PCIe 6.0 은 더 큰 비트수를 사용한다고 한다.

modem 안에 termination과 CTLE등 equalizer가 있고 여러 equalizer로 optimizing을 하는 것이다.

BER을 개선하기 위해서 또 여러 보정도 있다.

그러면서 DFE로 BER을 개선시키는데, 2-tap DFE로 hit map을 구현한 것이다.

확실히 equalizer에 대한 중요성이 있다. 이와 같이 equalizer와 timing recovery를 보면 위상을 조정하면서 보정을 한다.

이런 timing recovery latency에 영향도 고려해야한다.....

optical communication으로 넘어가서 광섬유 통신의 장점을 소개한다. loss 측면에서 우수하나 색분산에 대한 이슈가 존재한다. 이는 빛의 파장에 따른 분산인데, 역시 FIR filter로 보정이 필요하다.

광통신에 대한 얘기는 조금 어려워서 넘어가려고 한다. OMA로 노이즈를 견디는 것에 대한 식도 있으며 driver나 package 측면도 고려해서 봐야한다.

PAM4에 관한 간단한 이야기를 또 해보자면, ADC 부분과 FFE와 같은 equalizer의 요소로 구성되어서 pre-cursor와 post-cursor를 제거를 하며 해결을 하는 것이 있다.

나는 pre-cursor와 post-cursor를 처음 접했을 때, 무슨 말인지 어려웠었는데, 이는 ISI를 알아야 이해가 된다. 신호를 전달하는 과정에서 고속일수록 주변의 신호에 영향이 커서 pre와 post의 신호에 0/1을 구분하기 어렵게 노이즈가 끼기에 이를 제거하는 것을 말한다.

그런 제거하는 것의 측정으로 peak to main ratio가 있다. main의 값이 주변에 비해 커야 구분이 되는 것이다.

그래서 ADC의 quantization 크기가 range로 있다.

뭐 어찌됐든, 여러 FFE들이 tap에 따라서 다른 회로 구성이 있다. A2D에 흐름에 equalizer가 붙어서 loss를 해결하고 DSP에서 signal을 처리한다. 이런 여러 equalizer들이 중요하다.

이런 EQ부분은 또 다시 봐야할 것 같다. 아마 논문을 통해서 보는게 젤 best이지 않을까 싶다..... 어렵당

추가로 serdes에 관한 영상을 몇개 봐서 간단히 정리를 했었는데, 이 영상은 영상처리에 관련된 부분이었다. camera와 관련되었고 current mode dirver와 같은 부분과 jitter와 eye diagram에 대한 간략한 얘기를 한다.

또한 encoding에 관한 얘기로 DC balance로 1과 0의 disparity가 없게 한다고 한다.

LVDS serdes는 결국 chip to chip 통신으로 impedance matching과 CDR에 관해서 고려를 할 부분이라고 한다.

serdes의 PHY layer에 대한 것이 결국 하나의 protocol로 USR/XSR등이 있는 것이다. 즉 physical layer로써 존재하는 것이다.

그래서 PCIe를 보면 layer들로 회로가 구성되어 있는 것이다.

link equalization으로 packet 교환과 device의 layer, port, link에 대한 layer process가 있다.

두 device의 통신에서 sequence를 교환해서 state flow로 처리를 하는 것이다.

직렬통신으로 고속으로써 gen3 이상에서는 128b/130b encoding을 이용한다고 한다.

여러 layer 중에서 transaction layer는 software layer 요청으로 outbound packet을 생성하고, 구성요소로 TLP (transaction layer packet) 가 있어서 error detect를 하는 역할도 있다.

post와 non-post형태로 Tx에서 TL packet을 보내면 응답에서도 packet을 보내는 것이 non-packet이다.

그렇게 여러 layer들이 역할에 따라서 있고 protocal에 따르게 된다. 이런 규격이 있는 것이 interface로 layer 회로가 있는 것이다.

gen 3에서 3 tap Tx EQ (fir filter)를 사용해서 과거와 또 이전의 과거 모두 영향을 줘서 pre cursor를 제거하는 de-emphasis를 사용했다고 한다.

4가지의 volatge가 있고 CTLE와 같은 EQ로 보상하고 하는 것이다.

PCIe도 결국에 interface 그 자체로 통신을 하는 layer인 것이다. 즉... serdes....

마찬가지로 interfeace USR/XSR PHY 도 그냥 규격인 셈이다.

data center로 넘어가서 보면 Top of rack과 end of row로 나뉘는 것 같다.

ToR을 중심적으로 봐야할 것 같은데, Rack의 상단 설치로 cooper 길이는 짧다고 한다.

switch가 서버 설치된 걸로 이 switch가 컨트롤하는 것이다.

Rack안에 switch로 외부 ETH aggregation으로 엮는 것이다.

EoR은 끝에서 통합을 하는 switch로 구성되어 있다.

관리할 스위치가 적은 것이 장점이고, aggregation port수도 적은 것이다.

ToR은 sercer와 switch가 direct로 cooper inside형태로 cost 저렴이다. cable 수도 적고 rack을 분리/관리 형태로 쉽게 대처가 가능하다. fiber cable로 직접 aggregation switch에 관리하는 것이다.

EoR은 cable이 많고 group의 느낌으로 aggregation switch 직접연결로 파워소모가 크다고 한다.

이렇게 공부를 했었고 의문 사항에 대해서 정리를 해보면

1. pcie가 결국에 serdes를 사용하는 interface로 내부 회로적 구성이 비슷한지?=> PCIe gen1~gen5 (최신 칩셋에 gen5 (32Gb/s or 32G transfer/lane) 링크가 들어가고 있음)까지는 32Gb/s NRZ, gen6은 64Gb/s PAM-4 이며 구조는 현재 유력한 것이 ADC-DSP기반 SerDes임. PCIe SerDes는 가장 대중적으로 타겟이 되는 long-reach SerDes임2. serdes를 보니 on chip의 data rate이 느리고 off chip이 빠르게 구성을 하는데, on-chip에 고속으로 data rate을 뽑는 것이 제한이 되어있는지? off-chip이 더 빠를 수 밖에 없는지?=> 칩 안에서는 수백, 수천개의 병렬 레인에서 데이터가 GHz오더로 생성될 수 있으나, off-chip으로는 패드 수의 제한 등 물리적인 이유로 인해 직렬화하여 칩간 통신을 해야 함. 병렬->직렬 과정을 거치므로 throughput이 동일하다면 레인당 data rate이 빨라야만 함.3. ber을 시뮬레이션으로 확률을 나타내는데, 이에 대한 수식이 존재하는 건지? 구체적으로 살펴봐야하는지?=> BER은 보통 실제 측정을 통해 얻음. 수식적으로 할 수 있으나 (SNR기반으로 BER을 계산하는 Q function 등) 통계적인 것이고 실제로는 측정을 통해 BER bathtub curve 등을 구함.4. EQ라는게 결국에 그냥 필터만을 활용하는 것인지? 필터 회로를 pole과 zero에 맞춰서 구성만 하면 되는 건지 원리가 정확히 헷갈림...

=> PAM 변조방식에서는 사실상 대부분 아날로그 + 디지털 필터 조합의 equalization을 함. EQ는 linear (CTLE(아날로그), FFE(아날로그 or 디지털)), non-linear (DFE) equalization 등이 있음. 실제 널리 활용되는 것은 필터 기반이나, MLSE등의 sequence estimation방식을 적용한 링크도 존재함 (예: Nvidia A100 GPU의 50Gb/s NVLink SerDes: ADC-DSP based MLSE equalizer RX)

이렇다...

질문

공부할것

핵심

'MS Dairy > MS study' 카테고리의 다른 글

SerDes 2/24 (0) 2023.02.24 SerDes 2/22 (0) 2023.02.22 Power Integrity - real world (0) 2023.02.16 Power Integrity - overview (0) 2023.02.16 Signal Integrity - SI analysis (0) 2023.02.16